Le service de microélectronique de l’APC développe des circuits intégrés ASIC (Application Specific Integrated Circuit) pour la mise en œuvre d'instruments dédiés à la cosmologie observationnelle et aux expériences d’astroparticules.

Présentation de l'équipe :

Ce service est constitué de deux ingénieurs de recherche permanents : Fabrice Voisin, en poste depuis 2003, actuellement chef du service de microélectronique, rattaché aux projets QUBIC et WFEE ATHENA ; Damien Prêle, en poste depuis 2007, rattaché au projet QUBIC et chef de projet WFEE ATHENA.

En septembre 2015, Cyril Beillimaz a rejoint le service, bénéficiant d’un CDD financé par le CNES pour mener à bien la phase A du projet WFEE ATHENA. Depuis septembre 2016, Si Chen, doctorant co‑encadré par Damien Prêle, participe également aux développements des circuits intégrés dans le cadre de ce même projet.

Domaine d’expertise :

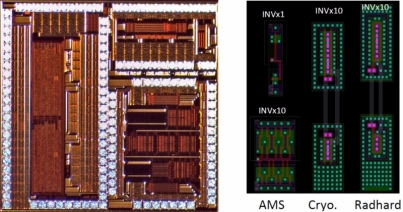

Le service de microélectronique de l’APC dispose de compétences en conception "full‑custom" d’ASIC "front‑end" analogiques et mixtes utilisant des technologies standards CMOS et BiCMOS du commerce pour des applications à température ambiante ou à très basses températures.

En particulier, les membres de ce service ont développé depuis une dizaine d’années une expertise spécifique au sein de l’IN2P3 dans le domaine de la conception d’ASIC ultra-bas-bruit (0,2 nV/√Hz), opérant en milieu cryogénique (4,2 K) pour l’intégration de senseurs supraconducteurs (TES, SQUID) ou durcis aux environnements radiatifs pour des applications spatiales.

Au cours des cinq dernières années, le service a également participé au développement de matrices de SPAD (Single Photon Avalanche Diode) pour la réalisation d’imageurs sensibles au photon unique en technologie ASIC CMOS standard.

Projets :

QUBIC (Q&U Bolometric Interferometer for Cosmology) :

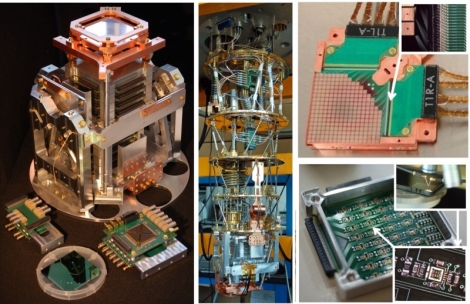

Le service a développé, dans le cadre d’activités de R&D liées au laboratoire millimétrique de l’APC, une expertise dans le domaine des multiplexeurs temporels à SQUID (Superconducting QUantum Interference Device) pour la lecture de grandes matrices de TES (Transition‑Edge‑Sensors) à l’aide de circuits intégrés ultra‑bas-bruit fonctionnant à température cryogénique.

Cette solution développée notamment dans le cadre de la R&D BSD est particulièrement innovante pour les instruments dédiés à la cosmologie observationnelle qui intègrent des systèmes de détection cryogéniques complexes ultra-sensibles et qui requièrent un fort taux de multiplexage.

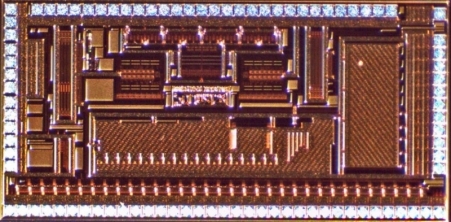

Deux ASIC ont été réalisés, l’un en 2012 (ʺSQMUX128ʺ) dans le cadre de l’intégration et la validation d’un quart de la chaîne de détection QUBIC dans un cryostat à dilution (2015) et le second en 2016 (ʺSQMUX128_evoʺ) en vue d’équiper le démonstrateur de l’instrument final dans son cryostat dédié (2017).C’est dans ce contexte que le service de microélectronique a pris en charge la réalisation et la qualification des ASIC équipant la chaîne de détection cryogénique du télescope QUBIC (deux plans focaux de 1024 TES chacun), expérience internationale d’interférométrie au sol dans le domaine des ondes millimétriques et submillimétriques (150 GHz et 220 GHz) pour l’étude des modes B de polarisation du fond diffus cosmologique (CMB pour Cosmic Microwave Background).

Ces ASIC mettent en œuvre un multiplexage temporel de 4 colonnes de 32 SQUID en séries pour la lecture de 128 TES. Ils intègrent un amplificateur ultra‑bas bruit (0,2 nV / √Hz) à 4 entrées multiplexées, 32 sources de courant multiplexées nécessaires à la polarisation des SQUID, un circuit numérique pour le séquencement de l’adressage et une liaison série pour paramétrer l’ensemble du circuit.

Outre la réalisation de ces ASIC fonctionnant à température cryogénique (4,2 K), le service de microélectronique est largement impliqué dans l’intégration de la chaîne de détection de l’instrument : définition et caractérisation des TES (détecteurs supraconducteurs à 300 mK) ; spécification, suivi de réalisation et test des SQUID (préamplificateur supraconducteur à 1 K) ; réalisation et intégration des modules de SQUID et d’ASIC (PCB) ; gestion des interconnections (bonding, câbles et connectique) ; spécification et interfaçage de l’électronique d’acquisition à chaud (300 K).

Ces réalisations d'ASIC fonctionnant aux très basses températures ont été proposées dans le cadre d'une collaboration internationale avec l'institut PMO (Purple Mountain Observatory, Chine) pour la mise en œuvre du plan focal d'un télescope situé à Dôme A en Antarctique. En 2013, le service de microélectronique a réalisé, testé et fourni à la collaboration un nouvel ASIC (ʺSQMUX24ʺ) intégrant les fonctionnalités nécessaires à la lecture et au multiplexage temporel de 24 TES. Un second ASIC est en préparation pour 2017 en vue d’équiper l’instrument final constitué de 1024 TES.

ATHENA (Advanced Telescope for High Energy and Astrophysics) :

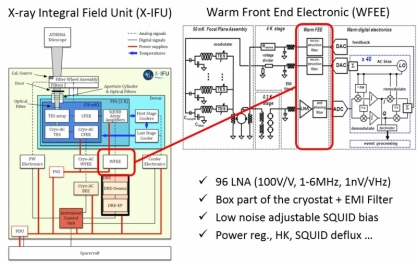

Dans le cadre de l’observatoire spatial ATHENA dans le domaine des rayons X, mission L2 de l’ESA, l’APC a la responsabilité du sous ensemble WFEE (Warm Front End Electronic) de l’instrument X‑IFU embarqué sur le satellite.

Le plan focal du détecteur X-IFU est composé de 3840 TES dont les signaux sont multiplexés en fréquence avec un taux de 40, soit un nombre de voies à amplifier puis à traiter réduit à 96.

La principale fonction du WFEE, situé à l’interface du cryostat et du DRE (Digital Readout Electronic), est d’intégrer sous la forme d’ASIC fonctionnant à 300 K les 96 voies d’amplifications (gain ultra‑stable 100V/V, 1-6MHz, 1nV/√Hz) et autant de sources de courant ajustables (DAC en courant) nécessaires à la polarisation des SQUID présents dans les étages cryogéniques ainsi qu’un lien série de type I2C ou RS485 pour le paramétrage de l’ensemble.

Le projet est actuellement dans sa phase A pour un lancement du satellite prévu en 2028.

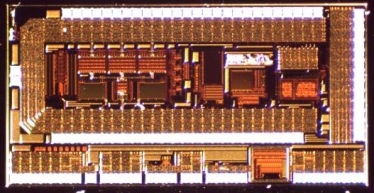

Un premier ASIC ("awaXe_v1") a été soumis en fonderie début 2016, incluant de nombreux véhicules de tests dans le but d’identifier les topologies compatibles avec les besoins du WFEE et de valider les techniques de durcissement aux radiations mises en œuvre pour la réalisation des cellules numériques.

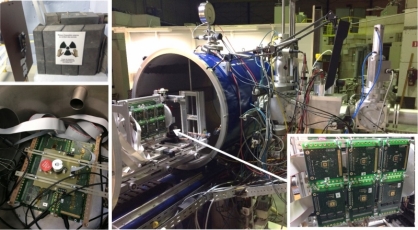

Le service de microélectronique a également pris en charge les phases de caractérisation de l’ASIC comprenant notamment une campagne de qualification en tenue aux radiations (dose et faisceau) ainsi que le développement des cartes (PCB) et bancs de tests associés.

Ces campagnes de tests aux radiations en dose (source au Cobalt 60 sur le site COCASE, CEA Saclay) et en faisceau (source Californium 252 dans les installations de la société TRAD et auprès du cyclotron de l’UCL Louvain) ont permis au service de microélectronique de disposer à présent d’une compétence indéniable en qualification spatiale.

Un deuxième ASIC ("awaXe_v2") est en cours de développement pour une soumission fin 2017 en vue d’une intégration de type "breadboard" pour la mise en œuvre d’un démonstrateur prévu en fin de phase A (2018).

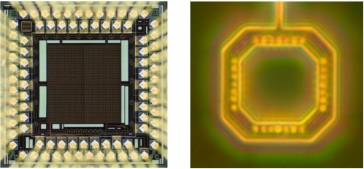

Le service de microélectronique a participé aux développements de matrices de SPAD (Single Photon Avalanche Diode) en technologie ASIC CMOS standard pour la réalisation d’imageurs sensibles au photon unique dans le cadre du projet Gamma Cube, R&D pour tracker gamma spatial. L’étude d’un système de codage et de multiplexage intégré à conduit à la réalisation, en 2014, d’un ASIC (ʺIMACUPʺ) dans le cadre d’une collaboration académique avec le LE2I (Laboratoire Electronique, Informatique et Image). Le service a également pris en charge la caractérisation de cette matrice de SPAD multiplexée ainsi que la réalisation du banc de test associé.

Ces travaux ont débouché sur une prospective de valorisation industrielle (SATT, Wtech) du concept de camera "gamma cube" pour des applications médicales.

Futurs projets :

Le service de microélectronique a pour vocation de répondre aux demandes des projets émergeant au laboratoire nécessitant son expertise. A ce titre, il participe activement aux prospectives de contribution au projet de satellite LiteBird ainsi qu’au projet d’instrument de quatrième génération S4 américain pour l’étude du CMB ou son équivalent européen E4.